FinFET

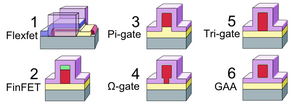

FinFET (Fin field-effect transistor, с англ. — «полевой транзистор с плавником»)[К 1] — МОП-транзистор, расположенный на полупроводниковой подложке, в котором затвор расположен с трёх или четырёх сторон канала или обёрнут вокруг него. Может представлять собой однозатворную структуру, чаще всего используется многозатворная[англ.]. FinFET с затвором, охватывающим канал с трёх сторон, иногда называется TriGate. Подобные транзисторы используются при производстве современных интегральных схем с проектными нормами меньше 22 нм.

Конструкция

В обычном планарном МОП-транзисторе (англ. Planar FET) канал располагается горизонтально. Когда в канале полем затвора формируется обращённый слой, подложка вытягивает часть носителей канала в обеднённый слой. В результате возникают статические токи утечки. Чтобы избежать подобного, можно расположить транзисторы на непроводящем основании, как это делается в КНИ-структурах. Однако подобная технология является сложной и достаточно дорогой, а также имеет ограничения по минимальной длине канала из-за короткоканальных эффектов[англ.][1].

В FinFET канал располагается не горизонтально, а вертикально, напоминая плавник (англ. Fin), и окружается с трёх сторон затвором. Площадь контакта канала с подложкой минимальна, что значительно сокращает статические токи утечки. Кроме того, подобная компоновка позволяет сократить площадь, занимаемую транзистором, поскольку канал достаточно узок в проекции. Например, ширина «плавника» FinFET фирмы Intel, изготовленного по проектной норме 14 нм, составляет 8 нм[1].

Чтобы увеличить протекающий ток и уменьшить сопротивление канала, увеличив быстродействие, в FinFET используют несколько параллельно расположенными «плавниками». В результате он представляет собой многозатворную структуру[англ.]. Кроме того, для улучшения характеристик транзистора, в качестве материала канала используют не кремний, который выступает только в качестве конструкционного материала для подложки, а выращенный SiGe, в котором носители заряда обладают большей подвижностью[1].

Однако одна из частей канала у FinFET всё равно контактирует с подложкой, поэтому всё равно возникают статические токи утечки. Чтобы избежать этого, в 2003 году была разработана GAAFET (Gate-All-Around FET, с англ. — «полевой транзистор, окружённый затвором со всех сторон»), в которой область канала превратилась в тонкую нанопроволоку, окружённую затвором с 4 сторон. Однако при этом в канале остаётся мало места для потока электронов, что ограничивает максимальный ток и замедляет скорость переключения транзистора. Для устранения этого недостатка была разработана структура NSFET (Nanosheet FET, с англ. — «нанолистовой полевой транзистор»)[1][2][3][4]. Фирма Samsung, которая начала использовать эту структуру в своих микросхемах, зарегистрировала для неё торговую марку MBCFET (Multi-Bridge Channel FET, с англ. — «полевой транзистор с многошлюзовым каналом»), в которой вместо нанопроволоки для канала использовалась стопка тонких листов кремния[5]. Фирма Intel для своего варианта структуры использует название RibbonFET[6].

История разработки FinFET

В 1967 году Г. Р. Фарра, работавший в Bendix Corporation[англ.], и Р. Ф. Стейнберг предложили концепцию двухзатворного тонкоплёночного транзистора[7]. В 1980 году Тосихиро Сэкигава из Электротехнической лаборатории[англ.] (ETL) запатентовал двухзатворный МДП транзистор[8], а в 1984 году совместно с Ютакой Хаяси изготовил его в ETL. При этом было продемонстрировано, что можно значительно уменьшить короткоканальные эффекты, если «зажать» полностью обеднённый КНИ-транзистор между двумя соединёнными между собой затворами[9][10].

Первый транзистор, который можно отнести к FinFET, был получен был создан в 1989 году в Центральной исследовательской лаборатории Hitachi (Япония) группой в составе Дига Ясамото, Тору Кага, Ёсифуми Кавамото и Эйдзи Такеда. Он получил название «транзистор с обеднённым узким каналом» (англ. depleted lean-channel transistor, DELTA)[9][11][12]. В 1996 году индонезийский инженер Эффенди Леобандунг, работавший в Миннесотском университете, сделал совместно со Стивеном Чоу доклад на 54-й Конференции по исследованию устройств, в котором описал преимущества разделения широкого канала КМОП-транзистора на множество узких каналов, что должно было улучшить масштабируемость и увеличить ток за счёт эффективного увеличения ширины устойства[13]. Подобная структура являлась прототипом современных FinFET. Отмечалось, что хотя из-за нарезки канала теряется часть его ширины, проводимость боковых стенок узких «плавников» при достаточной высоте более чем компенсирует эти потери[14][15]. Представленное устройство имело ширину канала в 35 нм и длину 70 нм[13].

Потенциал исследований транзисторов DELTA группой Дига Ясамото привлёк вниматие Управления перспективных исследовательских проектов Министерства обороны США (DARPA), которое в 1997 году заключило контракт с исследовательской группой Калифорнийского университета в Беркли на разработку субмикронных транзисторов на основе технологии DELTA[16]. Её возглавили Ясамото и Ченминг Ху[англ.] из TSMC. В итоге с 1998 по 2004 годы эта команда добилась следующих результатов[17]:

- 1998 год: создан n-канальный FinFET (17 нм)[18];

- 1999 год: создан p-канальный FinFET (менее 50 нм)[19];

- 2001 год: создан 15 нм FinFET[20];

- 2002 год: создан 10 нм FinFET[21];

- 2004 год: создан FinFET с высокопроницаемым подзатворным диэлектриком[англ.] и металлическим затвором[англ.].

Сам термин «FinFET» впервые был введён в научной статmt, опубликованной в декабре 2000 года[22], где описывался непланарный транзистор с двойным затвором, созданного на КНИ-подложке[23].

В 2006 году группа корейских учёных из Корейского института передовых технологий (KAIST) и Национального центра нанотехнологий разработала транзистор с проектной нормой 3 нм — самое маленькое на тот момент микроэлектронное устройство, основанное на технологии FinFET круглым каналом (GAAFET)[24][25]. А в 2011 году исследователи из Университета Райса Масуд Ростами и Картик Моханрам показали, что FinFET может иметь два электрически независимых затвора, что может дать разработчикам схем больше гибкости для создания эффективных транзисторов с низким энергопотреблением[26].

В 2020 году Ченминг Ху получил Медаль почёта IEEE за разработку FinFET, который, по оценке Института инженеров по электротехнике и электронике (IEEE), перевёл транзисторы в третье измерение и продлил действие закона Мура[27].

Коммерческий выпуск интегральных схем на FinFET

Первый в отрасли FinFET с проектной нормой 25 нм был продемонстрирован в декабре 2002 года компанией TSMC. Он был назван «Omega FinFET» из-за сходства формы затвора транзистора, охватывающего канал, с греческой буквой Ω[28].

В 2004 году фирма Samsung представила конструкцию «Bulk FinFET», которая сделала возможным массовое производство интегральных схем на подобных транзисторах. Первым таким устройством стал модуль динамической оперативной памяти (DRAM), содержащий FinFET с технологической нормой 90 нм[17].

В 2011 году компания Intel представила транзисторы с тремя затворами (TriGate), где затвор окружает канал с трёх сторон. Это позволило повысить энергоэффективность и снизить задержку, увеличиd производительность по сравнению с планарными транзисторами[29][30][31]. В этом же году был анонсирован микропроцессор Intel с микроархитектурой Ivy Bridge на трёхзатворных транзисторах с проектной нормой 22 нм[32]. Их коммерческий выпуск начался в 2012 году. Вскоре и другие крупнейшие производители интегральных схем (TSMC, Samsung, GlobalFoundries) начали использовать FinFET с проектными нормами 14 или 16 нм. В 2013 году SK Hynix запустила коммерческое массовое производство интегральных микросхем c FinFET с проектной нормой 16 нм[33], TSMS — тоже 16 нм[34], а Samsung — 10 нм[35].

Примечания

- Комментарии

- Источники

- ↑ 1,0 1,1 1,2 1,3 1,4 Технологические процессы изготовления электронной компонентной базы приборостроения. — С. 309—314.

- ↑ Kamal Y. The Silicon Age: Trends in Semiconductor Devices Industry (англ.) // Journal of Engineering Science and Technology Review. — 2022. — Vol. 15. — P. 113–114. — ISSN 1791-2377. — doi:10.25103/jestr.151.14.

- ↑ Mukesh S, Zhang J. A Review of the Gate-All-Around Nanosheet FET Process Opportunities (англ.) // Electronics. — 2002. — No. 11 (21): 3589. — doi:10.3390/electronics11213589.

- ↑ Максим Белоус. От плавников к кольцам и далее к КМОП: перипетии транзисторной эволюции. 3D News (30 декабря 2023). Дата обращения: 11 сентября 2025.

- ↑ 2022: Samsung begins shipping world's first 3nm chips. TADVISER. Дата обращения: 11 сентября 2025.

- ↑ Транзисторы достигают критической точки на уровне 3 нм. FAST TURN CHIP. Дата обращения: 11 сентября 2025.

- ↑ (February 1967) «Analysis of double-gate thin-film transistor». IEEE Transactions on Electron Devices 14 (2): 69–74. doi:10.1109/T-ED.1967.15901. .

- ↑ (23 February 2003) «Primary Consideration on Compact Modeling of DG MOSFETs with Four-terminal Operation Mode». TechConnect Briefs 2 (2003): 330–333.

- ↑ 9,0 9,1 Colinge, J. P. FinFETs and Other Multi-Gate Transistors : [англ.]. — Springer Science & Business Media, 2008. — P. 11 & 39. — ISBN 9780387717517.

- ↑ (August 1984) «Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate». Solid-State Electronics 27 (8): 827–828. doi:10.1016/0038-1101(84)90036-4. ISSN 0038-1101. .

- ↑ Hisamoto, Digh. A fully depleted lean-channel transistor (DELTA)-a novel vertical ultra thin SOI MOSFET // International Technical Digest on Electron Devices Meeting : [англ.] / Digh Hisamoto, Toru Kaga, Yoshifumi Kawamoto … [et al.]. — December 1989. — P. 833–836. — doi:10.1109/IEDM.1989.74182.

- ↑ IEEE Andrew S. Grove Award Recipients (англ.). IEEE Andrew S. Grove Award. Institute of Electrical and Electronics Engineers. Дата обращения: 4 июля 2019. Архивировано 9 сентября 2018 года.

- ↑ 13,0 13,1 Leobandung, Effendi. Reduction of short channel effects in SOI MOSFETs with 35 nm channel width and 70 nm channel length // 1996 54th Annual Device Research Conference Digest : [англ.] / Effendi Leobandung, Stephen Y. Chou. — 1996. — P. 110–111. — ISBN 0-7803-3358-6. — doi:10.1109/DRC.1996.546334.

- ↑ LeobandungEffendi. Nanoscale MOSFETs and single charge transistors on SOI (Ph.D. thesis). — Minneapolis, Minnesota: University of Minnesota, June 1996.

- ↑ (1997-11-01) «Wire-channel and wrap-around-gate metal–oxide–semiconductor field-effect transistors with a significant reduction of short channel effects». Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena 15 (6): 2791–2794. doi:10.1116/1.589729. ISSN 1071-1023. .

- ↑ The Breakthrough Advantage for FPGAs with Tri-Gate Technology (англ.). Intel (2014). Дата обращения: 4 июля 2019.

- ↑ 17,0 17,1 Tsu-Jae King, Liu FinFET: History, Fundamentals and Future (англ.). University of California, Berkeley. Symposium on VLSI Technology Short Course (11 июня 2012). Дата обращения: 9 июля 2019. Архивировано 28 мая 2016 года.

- ↑ Hisamoto, Digh. A folded-channel MOSFET for deep-sub-tenth micron era // International Electron Devices Meeting 1998. Technical Digest (Cat. No.98CH36217) / Digh Hisamoto, Chenming Hu, Tsu-Jae King Liu … [и др.]. — December 1998. — P. 1032–1034. — ISBN 0-7803-4774-9. — doi:10.1109/IEDM.1998.746531.

- ↑ Hisamoto, Digh. Sub 50-nm FinFET: PMOS // International Electron Devices Meeting 1999. Technical Digest (Cat. No.99CH36318) / Digh Hisamoto, Jakub Kedzierski, Erik Anderson … [и др.]. — December 1999. — P. 67–70. — ISBN 0-7803-5410-9. — doi:10.1109/IEDM.1999.823848.

- ↑ Hu, Chenming. Sub-20 nm CMOS FinFET technologies // International Electron Devices Meeting. Technical Digest (Cat. No.01CH37224) / Chenming Hu, Yang-Kyu Choi, N. Lindert … [и др.]. — December 2001. — P. 19.1.1–19.1.4. — ISBN 0-7803-7050-3. — doi:10.1109/IEDM.2001.979526.

- ↑ Ahmed, Shibly. FinFET scaling to 10 nm gate length // Digest. International Electron Devices Meeting / Shibly Ahmed, Scott Bell, Cyrus Tabery … [и др.]. — December 2002. — P. 251–254. — ISBN 0-7803-7462-2. — doi:10.1109/IEDM.2002.1175825.

- ↑ (December 2000) «FinFET—a self-aligned double-gate MOSFET scalable to 20 nm». IEEE Transactions on Electron Devices 47 (12): 2320–2325. doi:10.1109/16.887014. .

- ↑ (May 2001) «Sub-50 nm P-channel FinFET». IEEE Transactions on Electron Devices 48 (5): 880–886. doi:10.1109/16.918235. .

- ↑ Still Room at the Bottom.(nanometer transistor developed by Yang-kyu Choi from the Korea Advanced Institute of Science and Technology ), 2006-04-01, <http://www.highbeam.com/doc/1G1-145838158.html>. Проверено 6 июля 2019.

- ↑ Lee, Hyunjin. Sub-5nm All-Around Gate FinFET for Ultimate Scaling // 2006 Symposium on VLSI Technology, 2006. Digest of Technical Papers : [англ.]. — 2006. — P. 58–59. — ISBN 978-1-4244-0005-8. — doi:10.1109/VLSIT.2006.1705215.

- ↑ (2011) «Dual-Vth Independent-Gate FinFETs for Low Power Logic Circuits». IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 30 (3): 337–349. doi:10.1109/TCAD.2010.2097310.

- ↑ How the Father of FinFETs Helped Save Moore's Law: Chenming Hu, the 2020 IEEE Medal of Honor recipient, took transistors into the third dimension (англ.), IEEE Spectrum (21 April 2020).

- ↑ Fu-Liang Yang et al. 25 nm CMOS Omega FETs (англ.) // Digest. International Electron Devices Meeting. — San Francisco, 2002. — P. 255-258. — doi:10.1109/IEDM.2002.1175826.

- ↑ Bohr, Mark; Mistry, Kaizad Intel's Revolutionary 22 nm Transistor Technology (англ.). intel.com (May 2011). Дата обращения: 18 апреля 2018.

- ↑ Grabham, Dan. Intel's Tri-Gate transistors: everything you need to know (англ.), TechRadar (May 6, 2011-05-6).

- ↑ (2017) «CMOS Scaling Trends and Beyond». IEEE Micro 37 (6): 20–29. doi:10.1109/MM.2017.4241347. “The next major transistor innovation was the introduction of FinFET (tri-gate) transistors on Intel's 22-nm technology in 2011.”

- ↑ Intel 22nm 3-D Tri-Gate Transistor Technology (англ.). Intel Newsroom (2 мая 2011). Дата обращения: 6 мая 2018. Архивировано 6 мая 2018 года.

- ↑ History: 2010s (англ.). SK Hynix. Дата обращения: 8 июля 2019. Архивировано 17 мая 2021 года.

- ↑ 16/12nm Technology (англ.). TSMC. Дата обращения: 30 июня 2019.

- ↑ Samsung Mass Producing 128Gb 3-bit MLC NAND Flash (англ.), Tom's Hardware (11 April 2013).

Литература

- Технологические процессы изготовления электронной компонентной базы приборостроения: учеб.пособие / Д. В. Андреев, А. Е. Курносенко, В. В. Макарчук, В. А. Соловьев. — М.: Изд-во МГТУ им. Н. Э. Баумана, 2023. — 467 с. — (Библиотека «Приборостроение», Том. 1). — ISBN 978-5-7038-3493-0. — ISBN 978-5-7038-3509-8.

Ссылки

- Максим Белоус. От плавников к кольцам и далее к КМОП: перипетии транзисторной эволюции. 3D News (30 декабря 2023). Дата обращения: 11 сентября 2025.