Иерархия памяти

Иерархия компьютерной памяти — концепция построения взаимосвязи классов разных уровней компьютерной памяти на основе иерархической структуры.

Сущность необходимости построения иерархической памяти — необходимость обеспечения вычислительной системы (отдельного компьютера или кластера) достаточным объёмом памяти, как оперативной, так и постоянной.

Учитывая неоднородность периодичности обращения к конкретным записям (внутренним регистрам процессора, кэш-памяти, страницам и файлам) применяются различные технические решения, имеющие отличные характеристики, как технические так ценовые и массо-габаритные. Долговременное хранение в дорогой сверхоперативной и даже оперативной памяти, как правило, не выгодно, поэтому данные такого рода хранятся на накопителях — дисковых, ленточных, флеш и т. д.

Для обеспечения резервирования данных, например с целью сохранности, пользователи могут создавать библиотеки на съёмных носителях (например, виртуальная ленточная библиотека или дисковый массив), наполняя их своими файлами различных форматов. Доступ к этим данным занимает самое большое время, но при этом их ёмкость огромна.

В основном, техническими характеристиками служат временные, то есть каким временным критериям устраивает конкретное решение. Потребность в скоростной памяти, как правило лимитируется либо высокими накладными расходами по обеспечению работы схем, либо высоким энергопотреблением либо высокой стоимостью решения.

Различные виды памяти образуют иерархию, на различных уровнях которой расположены памяти с отличающимися временем доступа, сложностью, стоимостью и объёмом. Возможность построения иерархии памяти вызвана тем, что большинство алгоритмов обращаются в каждый промежуток времени к небольшому набору данных, который может быть помещен в более быструю, но дорогую и поэтому небольшую, память (см. en:locality of reference). Использование более быстрой памяти увеличивает производительность вычислительного комплекса. Под памятью в данном случае подразумевается устройство хранения данных (запоминающее устройство) в вычислительной технике или компьютерная память.

При проектировании высокопроизводительных компьютеров и систем необходимо решить множество компромиссов, например, размеры и технологии для каждого уровня иерархии. Можно рассматривать набор различных памятей (m1,m2,…,mn), находящихся в иерархии, то есть каждый mi уровень является как бы подчиненным для mi-1 уровня иерархии. Для уменьшения времени ожидания на более высоких уровнях, низшие уровни могут подготавливать данные укрупненными частями с буферизацией и, по наполнению буфера, сигнализировать верхнему уровню о возможности получения данных.

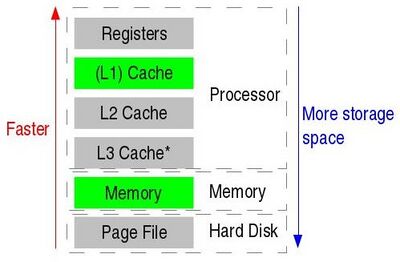

Часто выделяют 4 основных (укрупнённых) уровня иерархии:[1]

- Внутренняя память процессора (регистры, организованные в регистровый файл и кэш процессора).

- ОЗУ системы (RAM) и вспомогательных карт памяти.

- Накопители с «горячим» доступом (On-line mass storage) — или вторичная компьютерная память. Жесткие диски и твердотельные накопители, не требующие длительных (секунды и больше) действий для начала получения данных.

- Накопители, требующие переключения носителей (Off-line bulk storage) — или третичная память. Сюда относятся магнитные ленты, ленточные и дисковые библиотеки, требующие длительной перемотки либо механического (или ручного) переключения носителей информации.

В большинстве современных ПК используется следующая иерархия памяти:

- Регистры процессора, организованные в регистровый файл — наиболее быстрый доступ (порядка 1 такта), но размером лишь в несколько сотен или, редко, тысяч байт.

- Кэш процессора 1го уровня (L1) — время доступа порядка нескольких тактов, размером в десятки килобайт

- Кэш процессора 2го уровня (L2) — большее время доступа (от 2 до 10 раз медленнее L1), около полумегабайта или более

- Кэш процессора 3го уровня (L3) — время доступа около сотни тактов, размером от нескольких мегабайт до сотен

- Кэш процессора 4го уровня (L4) — время доступа несколько сотен тактов, размером одну-несколько сотен мегабайт. Применялся в процессорах Intel 5го поколения

- ОЗУ системы — время доступа от сотен до, возможно, тысячи тактов, но огромные размеры, от нескольких гигабайт до нескольких терабайт. Время доступа к ОЗУ может варьироваться для разных его частей в случае комплексов класса NUMA (с неоднородным доступом в память)

- Дисковое хранилище — многие миллионы тактов, если данные не были закэшированны или забуферизованны заранее, размеры до нескольких терабайт

- Третичная память — задержки до нескольких секунд или минут, но практически неограниченные объёмы (ленточные библиотеки).

Большинство программистов обычно предполагает, что память делится на два уровня, оперативную память и дисковые накопители, хотя в ассемблерных языках и ассемблерно-совместимых (типа C) существует возможность непосредственной работы с регистрами. Получение преимуществ от иерархии памяти требует совместных действий от программиста, аппаратуры и компиляторов (а также базовая поддержка в операционной системе):

- Программисты отвечают за организацию передачи данных между дисками и памятью (ОЗУ), используя для этого файловый ввод-вывод; Современные ОС также реализуют это как подкачку страниц.

- Аппаратное обеспечение отвечает за организацию передачи данных между памятью и кэшами.

- Оптимизирующие компиляторы отвечают за генерацию кода, при исполнении которого аппаратура эффективно использует регистры и кэш процессора.

Многие программисты не учитывают многоуровневость памяти при программировании. Этот подход работает пока приложение не столкнется с падением производительности из-за нехватки производительности подсистемы памяти. При исправлении кода (рефакторинг) необходимо учесть наличие и особенность работы верхних уровней иерархии памяти для достижения наивысшей производительности.

См. также

- Виртуальная память

- Компьютерная память

- Запоминающее устройство

- Иерархическое управление носителями

- Регистр процессора

- Регистровый файл

- Кэш

- Кэш процессора

- Оперативная память

- Запоминающее устройство с произвольным доступом

- Дисковый массив

- Прямой доступ к памяти

- Жёсткий диск

- Электронный диск

Литература

- Михаил Гук «Аппаратные средства IBM PC» Санкт-Петербург 1998

- Memory Hierarchy Design — Part 1. Basics of Memory Hierarchies, John L. Hennessy, 2012

Примечания

- ↑ Ty, Wing; Zee, Benjamin. Computer Hardware/Software Architecture (неопр.). — Bell Telephone Laboratories, Inc, 1986. — С. 30. — ISBN 0-13-163502-6.